Beágyazott rendszerek a mérnöki gyakorlatban

Molnár, András

Turóczi, Antal

Stojcsics, Dániel

Léczfalvy, Ádám

Kelemen, József

Somlyai, László

Beágyazott rendszerek a mérnöki gyakorlatban

írta Molnár, András, Turóczi, Antal, Stojcsics, Dániel, Léczfalvy, Ádám, Kelemen, József, és Somlyai, László

Tartalom

I. könyv. Digitális technikai alapáramkörök labormérése ... 1

1. Bevezetés ... 4

2. A mérés során használt eszközök ... 5

2.1. Spartan 3 FPGA család ... 5

2.1.2.1.1. Kapcsolómátrix ... 6

2.1.2.1.2. Órajel ... 6

2.1.2.1.3. Konfigurálható logikai blokk ... 6

2.1.2.1.4. Lookup table (LUT) ... 8

2.1.2.1.5. Erőforrások ... 10

2.2. Digilent Basys™2 Spartan-3E FPGA Board ... 11

3. Xilinx ISE fejlesztő rendszer ... 14

3.1. Első mintafeladat elkészítése – kapcsolási rajz alapú tervezés ... 16

3.1.3.1.1. Kapcsolási rajz készítése ... 19

3.1.3.1.2. A kapcsolás ellenőrzése szimulációval ... 21

3.1.3.1.2.3.1.2.1. Szimulációs fájl készítése ... 21

3.2. Makró hozzáadása meglévő projekthez ... 26

3.2.3.2.1. Példa kapcsolási rajz alapú makró készítésére ... 26

3.2.3.2.2. Kapcsolási rajz alapú saját makró módosítása ... 28

3.2.3.2.3. Kapcsolási rajz alapú saját makró hozzáadása projekthez ... 30

3.2.3.2.4. VHDL alapú saját makró hozzáadása projekthez ... 30

3.3. Kapcsolási rajz elkészítése a makró használatával ... 30

3.4. A kapcsolás hardveres ellenőrzése ... 32

3.4.3.4.1. A konfigurációs fájl letöltése az FPGA-ba ... 35

3.5. Az órajel bemenet prellmentesítése ... 35

4. Egyszerű kombinációs hálózatok ... 36

4.1. Multiplexer, demultiplexer ... 36

4.1.4.1.1. Multiplexer ... 36

4.1.4.1.1.4.1.1.1. 2 bemenetű multiplexer ... 36

4.1.4.1.1.4.1.1.2. 4 bemenetű multiplexer ... 37

4.1.4.1.2. Latch ... 41

4.1.4.1.3. Korrekt flip-flop órajel engedélyezés ... 41

4.1.4.1.4. Demultiplexer ... 42

4.1.4.1.5. Laborfeladat ... 43

4.1.4.1.5.4.1.5.1. Alkalmazandó műszerek és eszközök ... 44

4.2. Kódolók ... 44

4.2.4.2.1. Komparátorok (Magnitude Comparators) ... 44

4.2.4.2.2. Enkóderek ... 46

4.2.4.2.3. Prioritáskódoló (priority encoder) ... 47

4.2.4.2.4. Dekóder ... 50

4.2.4.2.4.4.2.4.1. 4-ről 1-re dekóder engedélyező jellel ... 50

4.2.4.2.5. Laborfeladat ... 51

4.2.4.2.5.4.2.5.1. Alkalmazandó műszerek és eszközök ... 52

4.3. Összeadó áramkör ... 52

4.3.4.3.1. Teljes összeadó (full adder) ... 53

4.3.4.3.2. BCD összeadó ... 56

4.3.4.3.3. Laborfeladat ... 57

4.3.4.3.3.4.3.3.1. Alkalmazandó műszerek és eszközök ... 57

4.4. Aritmetikai és Logikai Egység (ALU) ... 57

4.4.4.4.1. ALU blokkvázlata ... 58

4.4.4.4.2. ALU műveletvégző egységei ... 58

4.4.4.4.3. Laborfeladat ... 62

4.4.4.4.3.4.4.3.1. Alkalmazandó műszerek és eszközök ... 64

4.5. Shift regiszter ... 64

4.5.4.5.1. Léptető regiszterek ... 64

4.5.4.5.1.4.5.1.1. Soros-párhuzamos átalakító ... 64

4.5.4.5.1.4.5.1.2. Párhuzamos-soros átalakító ... 65

Beágyazott rendszerek a mérnöki gyakorlatban

4.5.4.5.1.4.5.1.3. Jobbra-balra léptető regiszter ... 65

4.5.4.5.1.4.5.1.4. Barrel shifter ... 65

4.5.4.5.2. Egyéb alkalmazások shift-regiszterrel ... 66

4.5.4.5.2.4.5.2.1. Lifo ... 66

4.5.4.5.2.4.5.2.2. A Johnson számláló ... 68

4.5.4.5.2.4.5.2.3. Soros összeadó ... 68

4.5.4.5.3. Laborfeladat ... 69

4.5.4.5.3.4.5.3.1. Alkalmazandó műszerek és eszközök ... 69

5. Négybites CPU tervezés ... 70

5.1. Bevezetés ... 70

5.1.5.1.1. Számítógépes architektúrák ... 70

5.1.5.1.2. Utasításkészlet ... 71

5.1.5.1.3. A labormérés alatt megépítendő CPU architektúrája ... 71

5.1.5.1.4. A CPU utasításainak felépítése ... 72

5.1.5.1.4.5.1.4.1. Az ’A’ és ’B’ regiszter bemenetének kiválasztása (Register input select) ... 73

5.1.5.1.4.5.1.4.2. ALU vezérlése (ALU control) ... 75

5.1.5.1.4.5.1.4.3. Ugró utasítások, a programszámláló megváltoztatása (Branch control) ... 77

5.1.5.1.4.5.1.4.4. Egyéb vezérlő jelek ... 80

5.1.5.1.4.5.1.4.5. Az utasítások felépítése ... 82

5.1.5.1.4.5.1.4.6. Mnemonik ... 82

5.1.5.1.4.5.1.4.7. A CPU teljes utasításkészlete ... 82

5.1.5.1.5. Laborfeladat ... 83

5.1.5.1.5.5.1.5.1. Alkalmazandó műszerek és eszközök ... 83

5.2. Órajel forrás, programszámláló, utasításregiszter, kijelzés ... 83

5.3. ALU és regiszterek ... 90

5.4. Kimeneti regiszterek, memória, ugró utasítás ... 97

5.5. Programkód írás ... 106

II. Könyv. Gadgeteer ... 110

6. ... 112

6.1. Kiknek szól a tananyag? ... 112

6.2. Miért .NETGadgeteer? ... 112

6.3. Szükséges előismeretek ... 112

7. Bevezetés a .NET Gadgeteer használatába ... 113

7.1. .NET Gadgeteeralkalmazások készítéséhez szükséges eszközök ... 113

7.2. FEZ Spider Starter Kit ... 113

7.3. A FEZ Spider demóapanel használata ... 116

7.4. Jelölések a demópanelen ... 116

7.5. Jelölések a próbamodulokon ... 117

7.6. A demópanel csatlakoztatása PC-hez ... 117

7.7. Egy egyszerű Gadgeteer program elkészítése ... 118

7.8. Felkészülést segítő kérdések ... 123

8. Stopper alkalmazás készítése .NETGadgeteer-el ... 125

8.1. A feladat célja ... 125

8.2. A projekt létrehozása ... 125

8.3. Az eszköz elkészítése ... 126

8.4. Az program megírása ... 128

8.4.8.4.1. Stopper osztály készítése ... 128

8.4.8.4.1.8.4.1.1. A főprogram elkészítése ... 132

8.5. A program futtatása ... 134

8.6. Felkészülést segítő kérdések ... 134

9. Fényerő szabályozó lámpa érintő kapcsoló .NETGadgeteer használatával ... 135

9.1. A feladat célja ... 135

9.2. A projekt létrehozása ... 135

9.3. A program megírása ... 136

9.4. A teljes forráskód ... 141

9.4.9.4.1. Felkészülést segítő kérdések ... 143

10. SD kártya olvasó .NET Gadgeteer használatával ... 144

10.1. A feladat célja ... 144

10.2. A projekt létrehozása ... 144

10.3. A program megírása ... 145

10.4. A teljes forráskód ... 152

10.5. Felkészülést segítő kérdések ... 154

10.6. Felhasznált irodalom ... 154

Irodalomjegyzék ... 155

Az ábrák listája

2.1. A Spartan-3 család belső felépítése [2] ... 5

2.2. Az órajel hálózat részei [1] ... 6

2.3. A szeletek elhelyezkedése a CLB-ben [2] ... 6

2.4. A szeletek összetevői [2] ... 7

2.5. LUT ... 8

2.6. Kapcsoló mátrix összeköttetések [2] ... 10

2.7. A részegységek FPGA-n belüli tömbszerkezete [2] ... 10

2.8. Digilent Basys™2 Spartan-3E FPGA panel [3] ... 11

2.9. Az Adept program konfigurációs felülete ... 11

2.10. Kapcsolók, nyomógombok és hétszegmenses kijelzők [3] ... 12

3.1. A tervezés menete [1] ... 14

3.2. Új projekt létrehozása ... 16

3.3. Új projekt létrehozása ... 17

3.4. A Project Navigator részei ... 18

3.5. A Symbols segédablak és a használt alkatrészek ... 19

3.6. Szimulációs fájl hozzáadása a projekthez ... 21

vhd-1. ../section/src/codeTestBrench1.vhd ... 22

vhd-2. ../sections/src/codeTestBrench2.vhd ... 23

3.7. A szimuláció eredménye a Xilinx ISE Simulator hullámforma ablakában. ... 25

3.8. Kijelzés formátuma ... 25

3.9. További jelek hozzáadása ... 26

3.10. Kapcsolási rajz módosítása ... 26

3.11. Elkészült makró kiválasztása ... 27

3.12. Top modul ... 27

3.13. Kimenet ... 28

3.14. Kapcsolási rajz alapú makró módosítása ... 29

3.15. Módosított szimbólumfájl ... 29

3.16. Makró szerkesztés ... 30

3.17. 8 bites számláló kapcsolási rajza ... 31

3.18. 8 bites számláló fájlok ... 31

vhd-3. ../sections/src/codeTestBrench3.vhd ... 31

3.19. 8 bites számláló szimulációs eredmény ... 32

3.20. A „Basys2_100_250General.ucf” fájl ... 33

vhd-4. ../sections/src/codeUcfClk4bit.vhd ... 33

3.21. UCF ... 34

vhd-5. ../sections/src/codeUcfClkPrell.vhd ... 35

3.22. A „teszt.sch” kapcsolási rajz módosítása ... 35

4.1. Két bemenetű multiplexer kapcsolási rajza ... 36

4.2. Két bemenetű multiplexer logikai rajza ... 36

4.3. Négy bemenetű multiplexer logikai rajza ... 37

4.4. Négy bemenetű multiplexer kapcsolási rajza ... 38

4.5. 16 bemenetű multiplexer tervezése kisebb multiplexerek felhasználásával ... 39

4.6. Look-up table megvalósítása multiplexer segítségével ... 40

4.7. Latch ... 41

4.8. Korrekt flip-flop órajel engedélyezés ... 42

4.9. Négy kimenetű demultiplexer ... 42

4.10. Négy kimenetű demultiplexer kapcsolási rajza ... 43

4.11. 2-szer 4-bites komparátor blokkrajza ... 44

4.12. Magnitude Comparator egy áramköri megvalósítása ... 45

4.13. 8_to_3 enkóder egy áramköri megvalósítása: ... 47

4.14. 8 bites prioritáskódoló rajzjele ... 48

4.15. 8 bites prioritáskódoló blokkrajza ... 49

4.16. A 8 bites prioritáskódoló megvalósítása 2×4 bitesből ... 49

4.17. 4-ről 1-re dekóder blokkrajza ... 50

4.18. 4-ről 1-re dekóder engedélyező jellel egy áramköri megvalósítása ... 51

4.19. Félösszeadó áramkör kapcsolási rajza ... 52

4.20. Teljes összeadó egy megvalósítása ... 53

4.21. Teljes összeadó egy megvalósítása ... 54

4.22. Teljes összeadó megvalósítása félösszeadó áramkörök segítségével ... 55

4.23. 4 bites összeadó áramkör ... 55

4.24. BCD összeadó ... 56

4.25. A laborgyakorlat során megépítésre kerülő ALU blokkvázlata ... 58

4.26. ALU ... 62

4.27. Gyűrüs számláló ... 64

4.28. Shift regiszter ... 64

4.29. Shift regiszter párhuzamos adatbemenettel ... 65

4.30. Jobbra-balra léptető regiszter ... 65

4.31. Fast, Compact Barrel Shifter with Encoded Shift Control ... 65

4.32. LIFO ... 66

4.33. Johnson számláló ... 68

4.34. Shift Register Applications Example: ... 69

5.1. Intel 80486-os processzor ... 70

5.2. Neumann és Harvard számítógép architektúra ... 71

5.3. A laborgyakorlatok alatt épített négybites CPU blokkvázlata ... 71

5.4. Az utasítások felépítése ... 82

5.5. Az utasítások felépítése ... 82

5.6. Utasításkészlet ... 82

5.7. A mintaprogram mnemonikjai és utasításkódjai ... 86

5.8. Ki-bemeneti egységek ... 86

5.9. A CPU műveletvégző egysége és regiszterei ... 90

5.10. A mintaprogram mnemonikjai és utasításkódjai ... 92

5.11. Ki-bemeneti egységek ... 92

5.12. A processzor blokkvázlatának részlete ... 98

5.13. A mintaprogram mnemonikjai és utasításkódjai ... 101

5.14. Ki-bemeneti egységek ... 101

5.15. Fordító program felépítése ... 107

5.16. Mintaprogram for ciklusra ... 107

vhd-6. ../sections/src/codeFor.vhd ... 108

5.17. Mintaprogram for ciklusra, hibaüzenettel ... 108

7.1. FEZ Spider Starter Kit ... 113

7.2. FEZ Spider demópanel ... 114

7.3. "Piros modul" ... 116

7.4. Csatlakozó aljzat a demópanelen ... 116

7.5. Csatlakozó aljzat a próbamodulon ... 117

7.6. Demópanelhez kapcsolt „piros modul” ... 117

7.7. Új projekt létrehozása ... 118

7.8. A létrehozni kívánt Gadgeteer projekt opciói ... 118

7.9. A létrehozott Gadgeteer projekt ... 119

7.10. A demópanel csere után ... 120

7.11. Próbamodulok a grafikus tervezőben ... 120

7.12. A demópanelra bekötött nyomógomb ... 121

7.13. A bekötött alkatrészek ... 121

7.14. A programkódot tartalmazó fájl kiválasztása ... 121

7.15. a program futtatás közben ... 123

8.1. Új projekt létrehozása ... 125

8.2. Projekt tulajdonságainak beállítása ... 125

8.3. Stopper készülék tervező nézetben ... 126

8.4. Új elem létrehozása a projektben ... 128

8.5. Új osztály hozzáadása a projekthez ... 128

8.6. Az új kódfájlban elhelyezett osztálydefiníció ... 129

8.7. A stopper állapotátmenet diagramja ... 131

8.8. Aprogram futtatás közben ... 134

9.1. A Visual Studio 2010 új .NETGadgeteer projekt ... 135

9.2. az összekötött rendszer ... 136

9.3. Teljesen kikapcsolt lámpa ... 139

Beágyazott rendszerek a mérnöki gyakorlatban

9.5. Teljesen felkapcsolt lámpa ... 141

10.1. A Visual Studio 2010 új .NET Gadgeteer projekt ... 144

10.2. az összekötött rendszer ... 145

10.3. a kezdőképernyő ... 147

10.4. a beolvasás folyamatábrája ... 147

10.5. csak txt-re keresés ... 150

10.6. minden fájlra keresés ... 151

10.7. nincs találat ... 152

A táblázatok listája

2.1. A függvény igazságtáblázata: ... 8

4.1. Egybemenetű multiplexer igazságtáblázata ... 36

4.2. Kétbemenetű multiplexer igazságtáblázata ... 37

4.3. Magnitude Comparator igazságtáblázata ... 44

4.4. Magnitude Comparator egyszerűsített igazságtáblázata ... 45

4.5. 8-ról 3-ra enkóder igazságtáblázata ... 46

4.6. 4 bites prioritáskódoló igazságtáblázata, (4.1), (4.2), (4.3) ... 47

4.7. 8 bites prioritáskódoló igazságtáblázata, (4.4), (4.5), (4.6), (4.7) ... 48

4.8. 4-ről 1-re dekóder igazságtáblázata ... 50

4.9. Portkiosztás ... 51

4.10. A két bites félösszeadó igazságtáblázata, (4.8), (4.9) ... 52

4.11. A két bites teljes összeadó igazságtáblázata, (4.10), (4.11) ... 53

4.12. Az ALU kimeneti jelei a vezérlőjeleinek függvényében ... 59

4.13. Portkiosztás ... 62

4.14. Johnson számláló igazságtáblázata ... 68

5.1. Az ’A’ és ’B’ regiszter bemenetének kiválasztása ... 73

5.2. ALU vezérlő jelei ... 75

5.3. Ugró utasítások ... 78

5.4. Kimeneti regiszterek vezérlő jelei ... 81

5.5. Kijelzők portkiosztása ... 84

5.6. Portkiosztás ... 87

5.7. Kimenet portkiosztása ... 91

5.8. Portkiosztás ... 93

5.9. Kijelzők portkiosztása ... 97

5.10. Ugró utasítások ... 99

5.11. Portkiosztás ... 102

Az egyenletek listája

4.1. (4.1) ... 48

4.2. (4.2) ... 48

4.3. (4.3) ... 48

4.4. (4.4) ... 48

4.5. (4.5) ... 48

4.6. (4.6) ... 48

4.7. (4.7) ... 48

4.8. (4.8) ... 52

4.9. (4.9) ... 52

4.10. (4.10) ... 53

4.11. (4.11) ... 53

I. könyv. rész - Digitális technikai

alapáramkörök labormérése

Tartalom

1. Bevezetés ... 4

2. A mérés során használt eszközök ... 5

2.1. Spartan 3 FPGA család ... 5

2.1.2.1.1. Kapcsolómátrix ... 6

2.1.2.1.2. Órajel ... 6

2.1.2.1.3. Konfigurálható logikai blokk ... 6

2.1.2.1.4. Lookup table (LUT) ... 8

2.1.2.1.5. Erőforrások ... 10

2.2. Digilent Basys™2 Spartan-3E FPGA Board ... 11

3. Xilinx ISE fejlesztő rendszer ... 14

3.1. Első mintafeladat elkészítése – kapcsolási rajz alapú tervezés ... 16

3.1.3.1.1. Kapcsolási rajz készítése ... 19

3.1.3.1.2. A kapcsolás ellenőrzése szimulációval ... 21

3.1.3.1.2.3.1.2.1. Szimulációs fájl készítése ... 21

3.2. Makró hozzáadása meglévő projekthez ... 26

3.2.3.2.1. Példa kapcsolási rajz alapú makró készítésére ... 26

3.2.3.2.2. Kapcsolási rajz alapú saját makró módosítása ... 28

3.2.3.2.3. Kapcsolási rajz alapú saját makró hozzáadása projekthez ... 30

3.2.3.2.4. VHDL alapú saját makró hozzáadása projekthez ... 30

3.3. Kapcsolási rajz elkészítése a makró használatával ... 30

3.4. A kapcsolás hardveres ellenőrzése ... 32

3.4.3.4.1. A konfigurációs fájl letöltése az FPGA-ba ... 35

3.5. Az órajel bemenet prellmentesítése ... 35

4. Egyszerű kombinációs hálózatok ... 36

4.1. Multiplexer, demultiplexer ... 36

4.1.4.1.1. Multiplexer ... 36

4.1.4.1.1.4.1.1.1. 2 bemenetű multiplexer ... 36

4.1.4.1.1.4.1.1.2. 4 bemenetű multiplexer ... 37

4.1.4.1.2. Latch ... 41

4.1.4.1.3. Korrekt flip-flop órajel engedélyezés ... 41

4.1.4.1.4. Demultiplexer ... 42

4.1.4.1.5. Laborfeladat ... 43

4.1.4.1.5.4.1.5.1. Alkalmazandó műszerek és eszközök ... 44

4.2. Kódolók ... 44

4.2.4.2.1. Komparátorok (Magnitude Comparators) ... 44

4.2.4.2.2. Enkóderek ... 46

4.2.4.2.3. Prioritáskódoló (priority encoder) ... 47

4.2.4.2.4. Dekóder ... 50

4.2.4.2.4.4.2.4.1. 4-ről 1-re dekóder engedélyező jellel ... 50

4.2.4.2.5. Laborfeladat ... 51

4.2.4.2.5.4.2.5.1. Alkalmazandó műszerek és eszközök ... 52

4.3. Összeadó áramkör ... 52

4.3.4.3.1. Teljes összeadó (full adder) ... 53

4.3.4.3.2. BCD összeadó ... 56

4.3.4.3.3. Laborfeladat ... 57

4.3.4.3.3.4.3.3.1. Alkalmazandó műszerek és eszközök ... 57

4.4. Aritmetikai és Logikai Egység (ALU) ... 57

4.4.4.4.1. ALU blokkvázlata ... 58

4.4.4.4.2. ALU műveletvégző egységei ... 58

4.4.4.4.3. Laborfeladat ... 62

4.4.4.4.3.4.4.3.1. Alkalmazandó műszerek és eszközök ... 64

4.5. Shift regiszter ... 64

4.5.4.5.1. Léptető regiszterek ... 64

4.5.4.5.1.4.5.1.1. Soros-párhuzamos átalakító ... 64

4.5.4.5.1.4.5.1.2. Párhuzamos-soros átalakító ... 65

4.5.4.5.1.4.5.1.3. Jobbra-balra léptető regiszter ... 65

4.5.4.5.1.4.5.1.4. Barrel shifter ... 65

4.5.4.5.2. Egyéb alkalmazások shift-regiszterrel ... 66

4.5.4.5.2.4.5.2.1. Lifo ... 66

4.5.4.5.2.4.5.2.2. A Johnson számláló ... 68

4.5.4.5.2.4.5.2.3. Soros összeadó ... 68

4.5.4.5.3. Laborfeladat ... 69

4.5.4.5.3.4.5.3.1. Alkalmazandó műszerek és eszközök ... 69

5. Négybites CPU tervezés ... 70

5.1. Bevezetés ... 70

5.1.5.1.1. Számítógépes architektúrák ... 70

5.1.5.1.2. Utasításkészlet ... 71

5.1.5.1.3. A labormérés alatt megépítendő CPU architektúrája ... 71

5.1.5.1.4. A CPU utasításainak felépítése ... 72

5.1.5.1.4.5.1.4.1. Az ’A’ és ’B’ regiszter bemenetének kiválasztása (Register input select) ... 73

5.1.5.1.4.5.1.4.2. ALU vezérlése (ALU control) ... 75

5.1.5.1.4.5.1.4.3. Ugró utasítások, a programszámláló megváltoztatása (Branch control) 77 5.1.5.1.4.5.1.4.4. Egyéb vezérlő jelek ... 80

5.1.5.1.4.5.1.4.5. Az utasítások felépítése ... 82

5.1.5.1.4.5.1.4.6. Mnemonik ... 82

5.1.5.1.4.5.1.4.7. A CPU teljes utasításkészlete ... 82

5.1.5.1.5. Laborfeladat ... 83

5.1.5.1.5.5.1.5.1. Alkalmazandó műszerek és eszközök ... 83

5.2. Órajel forrás, programszámláló, utasításregiszter, kijelzés ... 83

5.3. ALU és regiszterek ... 90

5.4. Kimeneti regiszterek, memória, ugró utasítás ... 97

5.5. Programkód írás ... 106

1. fejezet - Bevezetés

A könyv bevezetést kíván nyújtani a digitális áramkörök tervezésébe, célja a tervezési lehetőségek minél szélesebb körben való ismertetése. Manapság több módja is van az áramkörtervezésnek. A következőkben az FPGA alapú digitális áramkörtervezéshez szükséges ismeretekkel és eszközökkel ismerkedhetünk meg.

Ismertetésre kerül a XILINX cég SPARTAN 3 FPGA családja és a hozzá kiadott fejlesztői környezet. Valamint egy Basys 2 nevű FPGA fejlesztői kártya, aminek segítségével a megszerzett tudás kipróbálására islehetőség nyílik. A tananyag végén egy összetettebb projekt keretén belül, négybites CPU tervezésére és szimulációjára kerül sor.

2. fejezet - A mérés során használt eszközök

A következő részben az FPGA alapú tervezés alapjainak elsajátításához szükséges eszközök és szoftverek kerülnek ismertetésre. Természetesen a felsoroltak csak egy lehetőség, sok gyártó sokféle FPGA családot forgalmaz a különböző feladatok megoldására, valamint a tervezőszoftverekből is igen sokféle létezik.

2.1. Spartan 3 FPGA család

A Xilinx cég a 90 nm-es technológiával készült Spartan-3 FPGA családot olcsó, közepes bonyolultságú digitális áramkörök megvalósítására tervezte. A felhasználó a családon belül rengeteg különböző méretű, tulajdonságú és tokozású eszköz közül választhat igényeinek és az adott alkalmazásnak megfelelően. A Spartan-3 család öt alapvető programozható funkcionális elemből épül fel (2.1. ábra):

• Konfigurálható logikai blokkok (CLB-k): Logikai függvények és tároló funkció megvalósítására alkalmas elem.

• Input/Output blokkok (IOB-k): A be- és kimenetek (a külvilág) valamint a belső logika elemek közötti adatáramlást valósítják meg. Lehetővé teszik a kétirányú és háromállapotú (tri-state) interfészek valamint különböző szabványú és feszültségszintű digitális jelek illesztését.

• Blokk RAM: Adattárolásra alkalmas memória elem.

• Szorzó blokk (Multiplier): Két 18-bites bináris szám gyors összeszorzására alkalmas egység.

• Digitális órajel menedzser blokk (DCM): Az órajelek kezelésére szolgáló programozható egység.

Szolgáltatásai: késleltetés, frekvencia szorzás-osztás, fázistolás.

2.1. ábra - A Spartan-3 család belső felépítése [2]

A mérés során használt eszközök

2.1.2.1.1. Kapcsolómátrix

Az FPGA-n belül egy sűrű vezetékhálózat biztosítja az egyes elemek közötti kapcsolatot. A funkcionális blokkok programozható összeköttetéseken (kapcsoló mátrix) keresztül kapcsolódnak a vezetékhálózathoz. Az FPGA programja (konfigurációja) tulajdonképpen a funkcionális blokkok vezérlőjeleit valamint a kapcsolómátrixok állapotát határozza meg, vagyis, hogy a belső vezetékhálózaton keresztül mely egységek kerüljenek egymással összeköttetésbe. A programot az FPGA-n belül statikus konfigurációs memória tárolja, amelyet a tápegység bekapcsolása után a kívánt logikai funkciónak megfelelő adattal fel kell tölteni. A feltöltés történhet külső PROM-ból, külső mikroprocesszoron keresztül, vagy JTAG interfészen keresztül. A konfigurációs adat előállítását, a konfigurációs memóriák feltöltését, valamint a JTAG interfészen történő programozást a gyártó saját Xilinx ISE programcsomagja támogatja.

2.1.2.1.2. Órajel

Az órajelek FPGA-n belüli elosztásáért speciális belső vezetékhálózat felelős, amely a flip-flopok és egyéb órajeles működésű egységek órajel bemeneteihez kapcsolódik. Az órajel hálózathoz speciális bemeneti blokk (GCLK) és meghajtó-multiplexer (BUFGMUX) tartozik. A hálózatra kerülő órajelet a multiplexer választja ki a GCLK bemenetről vagy a DCM valamelyik kimenetéről (2.2. ábra).

2.2. ábra - Az órajel hálózat részei [1]

Az FPGA-n belül megengedett, hogy egy flip-flop egy általános felhasználású bemenetről vagy belső vezetékről kapja az órajelét, a nagy-sebességű szinkron működés biztosítása érdekében azonban ez nem javasolt.

2.1.2.1.3. Konfigurálható logikai blokk

A konfigurálható logikai blokkok (CLB-k) az elsődleges építő elemei az FPGA-ban felépített kombinációs vagy szinkron sorrendi hálózatoknak. A CLB-k egymással összeköttetésben lévő szeletekből (SLICE) épülnek fel (2.3. ábra).

2.3. ábra - A szeletek elhelyezkedése a CLB-ben [2]

A szeletek, típustól függően logikai és memória funkciót (SLICEM) vagy csak logikai funkciót (SLICEL) láthatnak el (2.4. ábra). Mindkét szelet tartalmazza az alábbi összetevőket:

• Két 4-bemenetű LUT

• Két tároló elem

• Két multiplexer

• Carry és aritmetikai logika

A SLICEM szeletek további összetevői:

• Két 16x1 bit RAM blokk

• két 16-bites shift-regiszter

2.4. ábra - A szeletek összetevői [2]

A mérés során használt eszközök

2.1.2.1.4. Lookup table (LUT)

A számítógép (sőt számológép) előtti időkben a bonyolultabb függvényeket egy könyv alakban kinyomtatott táblázat segítségével számították ki, ahol a függvény értékei bizonyos felbontásban és pontossággal voltak megadva, és a táblázatban megadott értékek között lineáris interpolációval számoltak (logaritmustáblák, trigonometrikus függvények, stb.). A megfelelő értékek kikeresése sokkal gyorsabb volt, mint a függvény valamilyen képlettel történő közelítő kiszámítása. Természetesen, valakiknek előzőleg ki kellett számolni a táblázat értékeit, sokszor sok-sok éves munkával. A számítástechnikában a használata azon alapul, hogy egy előre feltöltött tárolóból rendszerint sokkal gyorsabban lehet az adatokat kiolvasni, mint azokat valamilyen algoritmussal kiszámolni. A fixpontos és lebegőpontos aritmetikákban is használnak LUT-ota kezdeti pontosságú érték előállítására, a végső pontosságot már számítással érik el. Az FPGA CLB blokkjában a LUT az adott logikai függvény értékeit tartalmazza, amit a fordítóprogram a logikai rajz alapján állít elő és tárol el benne. 4 bemeneti változó esetén az összes lehetséges logikai függvény száma 64K. A következő példa az alábbi háromváltozós logikai függvény Look-Up-Table lel történő megvalósítását láthatjuk.

2.1. táblázat - A függvény igazságtáblázata:

ABCY 00000 10010 20101 30110 41001 51010 61101 71110

2.5. ábra - LUT

A mérés során használt eszközök

2.1.2.1.5. Erőforrások

Az FPGA erőforrásai (CLB, IOB, DCM, RAM és a szorzó) közötti kapcsolatot a kapcsoló mátrixok biztosítják (2.6. ábra). A kapcsoló mátrixok a belső vezetékhálózatra kapcsolódnak, ami horizontálisan és vertikálisan az egész FPGA-t lefedi, így – bizonyos megkötésekkel – bármely elem bármelyik másikkal összeköttetésbe hozható (2.6. ábra, 2.7. ábra).

2.6. ábra - Kapcsoló mátrix összeköttetések [2]

2.7. ábra - A részegységek FPGA-n belüli tömbszerkezete [2]

A Spartan-3 családról további információ a gyártó honlapján érhető el:

http://www.xilinx.com/support/documentation/spartan-3.htm

2.2. Digilent Basys™2 Spartan-3E FPGA Board

A mérés során a SPARTAN-3E típust tartalmazó demonstrációs panelt (Digilent Basys™2 Spartan-3E FPGA Board) fogjuk használni (2.8. ábra). A fejlesztőkártya paraméterei a következőek:

• Xilinx Spartan-3E FPGA, 100000 kapu

• 18-bites szorzók, 72Kbits dual-port block RAM

• USB 2 port az FPGA konfigurálásához (ingyenes Adept 2.0 szoftverrel)

• XCF02 Platform Flash ROM az FPGA konfiguráció tárolásához

• Programozható frekvenciájú oszcillátor (25, 50, and 100 MHz), egy további foglalat kvarc- oszcillátorhoz

• Stabilizált tápegységek (1.2V, 2.5V, and 3.3V)

• 8 LED, 4 db. hétszegmenses kijelző, 4 nyomógomb, 8 kapcsoló, PS/2 port, VGA port

• Felhasználói I/O csatlakozók

2.8. ábra - Digilent Basys™2 Spartan-3E FPGA panel [3]

A panelt a hozzá tartozó USB kábel segítségével csatlakoztatjuk a PC-hez. Bár lehetőség van külső tápforrás bekötésére, a tápellátás és a programozás is az USB kábelen keresztül történik. A panel be- és kikapcsolása az SW8 jelű kapcsolóval végezhető. A programozásához szükséges (.bit kiterjesztésű) konfigurációs állományt – amelyet a későbbiekben ismertetett Xilinx ISE fejlesztő rendszerrel állítunk elő – a panel gyártója által ingyenesen hozzáférhető Adept segédprogram segítségével tölthetjük le közvetlenül az FPGA-ba, vagy a hozzá kapcsolódó külső konfigurációs PROM-ba (Platform Flash). A program kezelői felületét az alábbi ábrán látható (2.9. ábra). A közvetlenül az FPGA-ba töltött konfiguráció a tápfeszültség kikapcsolása után törlődik, a következő bekapcsolást követően az FPGA a Platform Flash-ben tárolt állomány szerint konfigurálódik fel automatikusan. A négy nyomógomb bemenet alapállapotban logikai „0” (L) szinten van. Logikai „1” szint (H) a gomb megnyomásával adható a bemenetekre. A nyolc kapcsoló konstans „L” vagy „H” szintet ad a hozzájuk tartozó bemenetekre. A nyolc LED a hozzájuk tartozó kimenetek logikai „1” szintje esetén világítanak (2.10.

ábra).

2.9. ábra - Az Adept program konfigurációs felülete

A mérés során használt eszközök

A négy hétszegmenses kijelző szegmensei és a tizedes pont multiplexált módban vezérelhetők. A CA, CB, CC, CD, CE, CF, CG és DP jelekkel a szegmenseket és a tizedes pontot kapcsolhatjuk ki/be. Az AN0, AN1, AN2 és AN3 jelekkel választhatjuk ki, hogy a négy kijelző közül melyikre vonatkoznak a szegmenseket vezérlő jelek. A vezérlő és kiválasztó jelek megfelelően gyors egymás utáni kapcsolgatásával négydigites számokat jelezhetünk ki.

2.10. ábra - Kapcsolók, nyomógombok és hétszegmenses kijelzők [3]

3. fejezet - Xilinx ISE fejlesztő rendszer

A Xilinx ISE WebPack (Integrated Software Environment – integrált szoftverkörnyezet) a Xilinx cég FPGA- ihoz és CPLD-ihez kifejlesztett ingyenes szoftvere, amely az internetről, a cég weboldaláról szabadon letölthető.

A fejlesztőrendszer tartalmazza mindazon elemeket, amelyek kapcsolási rajz alapú és hardverleíró nyelv alapú fejlesztéshez szükségesek. A mérési segédlet bevezetést kíván nyújtani az áramkörök tervezésébe, célja a tervezési lehetőségek minél szélesebb körben való ismertetése. Elmélyülésre – a korlátozott laboridő miatt – saját munkával, illetve a konzultációk alatt van lehetőség. A mérések sikeres elvégzését nagymértékben segíti a mérést előkészítő előadás anyagának elsajátítása. Az ISE tervező rendszer alrendszereinek, részeinek működését a Project Navigator szoftver, az ISE keretprogramja fogja össze (3.1. ábra).

3.1. ábra - A tervezés menete [1]

A tervező az elképzeléseit, terveit:

• beviheti kapcsolási rajz (Schematic) formájában, a kapcsolási rajz készítő és beviteli program segítségével.

• beviheti hardver leíró nyelven. Ezt a HDL editor rész támogatja. A támogatott nyelvek: Verilog és VHDL. A rendszer sok mintaleírást is tartalmaz, úgynevezett sablonok (template) formájában.

A bevitel utáni az ellenőrzéssel megbizonyosodunk arról, hogy a terv szerinti áramkör működése megfelel-e a

Xilinx ISE fejlesztő rendszer

Xilinx ISE Simulator. A szimulációs vizsgálathoz a modellt működtetni, „gerjeszteni” kell, azaz a modell bemeneteire megfelelően változó jeleket kell adni. Ez az úgynevezett tesztvektorok sorozatának ráadásával történik. A tesztvektorokat a tervező HDL leírással adhatja meg (testbench). A régebbi ISE verziókban rendelkezésre álló grafikus felület az újabb verziókban már nem érhető el. Ha a tervet rendben találtuk, akkor következhet a szintézis, amit jelen esetben a Xilinx Synthesis Technology (XST) alrendszer végez, amely ugyancsak az ISE része. A szintézer a HDL leírásból előállít egy minimalizált és optimalizált huzalozási listát, amely az adott FPGA primitíveket (LUT, FF…) és a köztük levő kapcsolatokat tartalmazza. Ezt követik a Translate, a Map és a Place&Route fázisok (összefoglalva: implementáció). A Translate a huzalozási listákból és a felhasználói megkötésekből (constraint-ek) generál egy fájlt, a Map leképezi ezt az adott FPGA primitív- készletére, végül a Place&Route elhelyezi a primitíveket az eszközben és kialakítja a köztük levő fizikai huzalozást. A programozói fájl előállítását követő programozást normál esetben („égetés”) az IMPACT alrendszer vezérli. A mérések során használt demonstrációs panelhez a panel gyártója saját programozói felületet biztosít.

3.1. Első mintafeladat elkészítése – kapcsolási rajz alapú tervezés

A Xilinx ISE WebPack segítségével hozzunk létre egy egyszerű példaprogramot a gyakorlópanelen található LED-ek, kapcsolók és nyomógombok tesztelésére! A program ikonjára kattintva, vagy a Start menüből indítsuk el a Xilinx ISE Design Suite

ISE Design Tools

32-bit Project Navigator-t. A mintapélda projekt létrehozásához a File menüben válasszuk a New Project parancsot, és töltsük ki a párbeszédablakot az alábbi módon (3.2. ábra). Az ISE fejlesztő környezetben kerülni kell a fájlnevekben és a könyvtárszerkezetben a különleges karaktereket (ékezet, szóköz, vessző, pont, stb). A fájlok, könyvtárak lenevezésekor csak az angol ABC betüit használjuk!

• A Project Name legyen „proba”. A rendszer automatikusan létrehoz egy ilyen nevű mappát a Project Location mezőben megadott elérési útnak megfelelően. Az ISE a projekthez tartozó állományokat ebbe a mappába fogja menteni.

• Top-Level Module Type mezőben a legördülő ablakból válasszuk a Schematic-ot.

• A Next gombra kattintás után megjelenik a New Project Wizard, a Project Settings táblába írhatunk be paramétereket, válasszuk a próbapanelhez tartozó alábbi értékeket:

• Family: Spartan3E

• Device: XC3S100E

• Package: CP132

• Speed : -4

• Synthesis Tool: XST (VHDL/Verilog)

• Simulator: ISim (VHDL/Verilog)

3.2. ábra - Új projekt létrehozása

3.3. ábra - Új projekt létrehozása

Xilinx ISE fejlesztő rendszer

A többi paramétert most nem kell változtatnunk. A Next gombra kattintva megjelennek a készülő projekt adatai.

A Finish gombra kattintva elkészül a még üres próba projekt. Új modul létrehozásához a Project menüben kattintsunk a New Source parancsra, és válasszuk a Schematic típusú forrást. A létrehozandó modul neve legyen

„teszt”, amit a File name ablakba kell beírni, és jelöljük ki az Add to Project opciót. A Next majd Finish gombra kattintás után egy üres kapcsolási rajz szerkesztő jelenik meg, amiben elkészíthetjük a próbaalkalmazást. A View menüpont Panel alpontjában kijelölhetjük, hogy a szerkesztő ablakban mely segédablakok jelenjenek meg.

Egyelőre hagyjuk meg az alapértelmezés szerinti beállításokat. A jobb oldalon a rajzlap, a bal oldalon a Select Options jelenik meg. Itt a rajzolással kapcsolatos néhány paramétert állíthatunk be. Általában a képernyő az alábbi részekre van osztva (3.3. ábra, 3.4. ábra). Alul a Consol látható, ahol a parancsok szöveges formában jelennek meg.

3.4. ábra - A Project Navigator részei

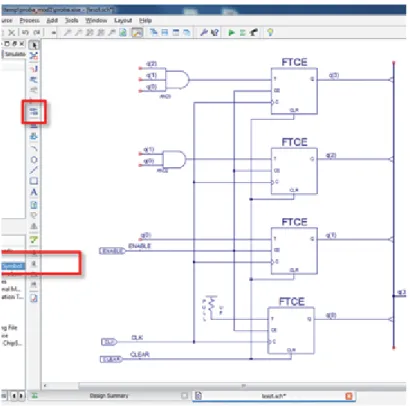

3.1.3.1.1. Kapcsolási rajz készítése

A tesztalkalmazásban egy T-tárolókból felépített 4-bites bináris számláló kapcsolást valósítunk meg. A számláló kimeneti bitjei a panelen található LED-eket hajtják meg, így ellenőrizhető a kapcsolás működése. A számlálót a Basys 2 FPGA fejlesztő kártyán található SW0 kapcsolóval engedélyezzük, a BTN0 nyomógombbal pedig nullázhatjuk. A segédablakok közül válasszuk a Symbols fület, ennek segítségével helyezhetjük el a kapcsolási rajzban használt alkatrészeket (3.5. ábra), felül a kategória, alatta a hozzátartozó egyik elem kiválasztásával:

• FTCE: Engedélyezhető T-flip-flop (4 db, a négybites számlálóhoz)

• AND3, AND2: három, ill. két bemenetű ’ÉS’ kapuk (a bemeneti kombinációs hálózathoz)

• PULLUP: Pozitív tápfeszültség (logikai magas jelszint (H))

• PULLDOWN: Földpont (logikai alacsony jelszint (L))

• CONSTANT: Jelnek vagy busznak konstans értékadás.

• IBUF: Egybites bemeneti buffer (több bites változatai: IBUF4, IBUF8, IBUF16)

• OBUF: Egybites kimeneti buffer (több bites változatai: OBUF4, OBUF8, OBUF16)

Az alkatrészek megkeresése történhet kategóriák (Categories) alapján, de használhatjuk a névkeresőt is (Symbol Name Filter). Az alkatrészek forgatását az Orientation mezőben állíthatjuk be.

3.5. ábra - A Symbols segédablak és a használt alkatrészek

Xilinx ISE fejlesztő rendszer

Az alkatrészek huzalozásakor a következő parancsokat, ill. parancsikonokat fogjuk használni:

• Select ( ): Kiválasztás/mozgatás.

• Add Wire ( ): Vezeték hozzáadása.

• Add Net Name ( ): Vezetékezés elnevezése.

• Rename Selected Bus ( ): A kijelölt busz átnevezése.

• Add Bus Tap ( ): Buszos vonalra csatlakozás hozzáadása.

• Add I/O Marker ( ): Be-, kimeneti pontok hozzáadása.

• Add Symbol ( ): Szimbólum (alkatrész, könyvtári, vagy saját) hozzáadása.

Mindegyik művelethez a bal alsó ablakban (Process/Options) találunk beállítási lehetőségeket, illetve műveleteket. A kényelmesebb szerkesztés érdekében megnövelhetjük a lap méretét is. Ezt a rajz területen jobb kattintásra felugró Object Properties parancs kiválasztásával tehetjük meg. A megjelenő ablakban a Sheets sort kiválasztva módosíthatjuk a lap méretét (Size). Vezeték vagy busz elnevezéséhez válasszuk az Add Net Name parancsot majd a bal alsó ablakban az Options fülnél a Name sorba írjuk a nevet. Ezután kattintsunk az elnevezni kívánt vezetékre. A vezetékek neveire a kapcsolási rajz átláthatósága érdekében is hivatkozhatunk, ugyanis ha két vagy több vezetéket ugyan úgy nevezünk el, az olyan, mintha fizikailag összehuzaloztuk volna őket (lásd az és kapuk bemeneteit és a tárolók kimeneteit). A tárolók q(0), q(1), q(2) és q(3) kimenetei a speciális q(7:0) un. buszvezetékre csatlakoznak (buszvezetékeket a kapcsolási rajzokban az összetartozó vezetékek ábrázolása érdekében használunk). A buszok, illetve leágazásaik elnevezése utal arra, hogy adott buszon belül melyik vonalra (bitre) csatlakozunk. Az előző példa (3.5.ábra) kapcsolásán a q(7:0) jel egy 8 bites busz, melyre az adott helyértékű bitvezeték (q(0)…q(7)) buszcsatlakozáson (Bus Tap) keresztül kapcsolódik. A kapcsolódás be- és kimeneti jelei I/O buffer-eken keresztül kapcsolódnak a külvilágot reprezentáló I/O Marker- ekhez. A CLK, ENABLE, és CLEAR bemenetekre IBUF, a LED(7:0) kimenetekre pedig OBUF (itt egy 8 bites OBUF8) elemeket helyezünk el, ez a szabályos megoldás. Az automatikus buffer-elhelyezés miatt a kapcsolás ezek nélkül is implementálható, de a be- és kimenetek nincsenek optimálisan bufferelve. Az IBUF és OBUF elemekkel számos beállítás mellett pl. a logikai családhoz, illetve a logikai szintekhez való illesztés valósítható meg. A rajz ellenőrzése az alsó Processes területen kibontva a Design Utilities-t, a Check Design Rules-ra kattintva fut le, ami ha jó, egy zöld pipa jelenik meg mellette. Ugyanezt tehetjük meg a Tools > Check Schematic paranccsal.

3.1.3.1.2. A kapcsolás ellenőrzése szimulációval

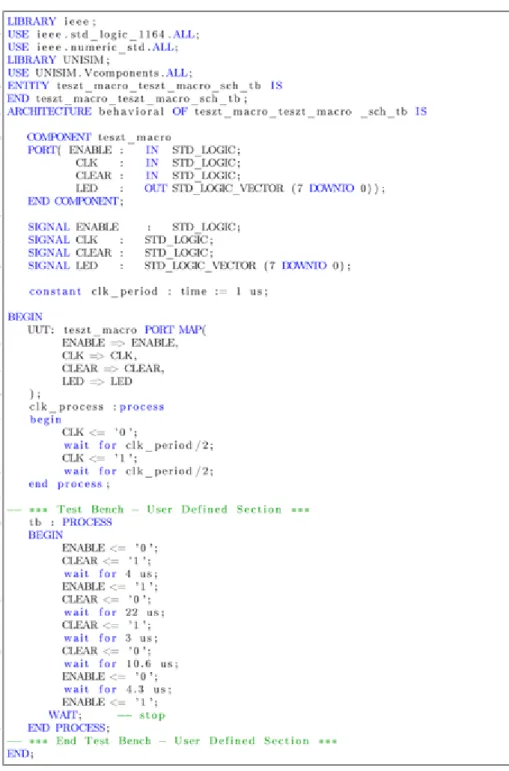

Teszteljük le a kapcsolás működését szimulációval! Ehhez létre kell hoznunk egy ellenőrzési környezetet (testbench, tesztelési környezet) melyben az egységet működtető gerjesztő jeleket és jelformákat definiáljuk.

Régebbi ISE verziókban lehetőség volt a gerjesztő-jelek grafikus felületen történő megadására, az újabb verziókból azonban kikerült ez a funkció, így az egyetlen lehetőség a HDL nyelvű leírás. A gyakorlatokon nem cél a HDL nyelvek ismertetése, ezért a tesztkörnyezetet leíró forrást nem kell elkészíteni, a kész forrásokat csak a projekthez kell adni.

3.1.3.1.2.3.1.2.1. Szimulációs fájl készítése

Az elkészült projekthez szimulációs fájlt a „Design/Simulation” ablakban, az „Add New Source” opcióval lehet hozzáadni (3.6. ábra). Fontos hogy minden port nevet adjunk meg a kapcsolási rajzon a szimulációs fájl elkészítése előtt, mert a program az aktuális port neveket használja fel a sablon elkészítésére.

3.6. ábra - Szimulációs fájl hozzáadása a projekthez

Xilinx ISE fejlesztő rendszer

Ezután a „VHDL Test Bench” opciót válasszuk és adjuk meg a tesztfájl nevét (teszt_tb). A „Next” gomb lenyomása után a program megkérdezi melyik forrásfájlhoz készül a tesztfájl. Itt válasszuk a fő kapcsolási rajzot (példánkban: teszt.sch), majd válasszuka „Next” gombot, végül kattintsunk a „Finish” gombra. Az ISE által generált sablon fájl tartalmazza a ki- és bemeneti portokat és a VHDL fájl keretét. Ha mindent jól csináltunk a következő VHDL fájlt kapjuk eredményül:

vhd-1. ábra - ../section/src/codeTestBrench1.vhd

A vizsgálójelek előállításához az alapértelmezett tesztfájlt módosítani kell. Az első kiegészítéssel adjuk hozzá a szimulációhoz a számlálót működtető 1MHz-es órajelet (CLK). A kódba a constantclk_period : time :=1us; sor beszúrásával definiálásra kerül az órajel periódusideje és a clk_process : processbegin.…end process-el az órajel előállításra kerül. Amennyiben nem CLK az órajel port neve, módosítani kell az általunk használt névre. A fenti kiegészítéseket elvégezve, a szimuláció során a CLK bemeneti porton egy 1 us periódusidejű órajel jelenik meg.

vhd-2. ábra - ../sections/src/codeTestBrench2.vhd

Xilinx ISE fejlesztő rendszer

A jeleknek értéket a "<=" értékadó utasítással lehet adni (példa: ENABLE<=’1’). Buszvezetékeknél értékadás binárisan történik (példa egy négybites busz értékadására: INB<="1011"). A jelek beállítása után a wait for paranccsal adhatjuk meg mennyi ideig maradjanak meg a beállított értékek. Lehetőség van kész VHDL testbench-et hozzáadni a projekthez. A "valami_tb.vhd" fájlt ami tartalmazza a szimulációs környezetet, célszerű a projekt könyvtárába másolni, majd a Project menü Add Source parancsával adhatjuk hozzá a projekthez. A megjelenő Adding Source Files ablakban az Association alatt a Simulation kell, hogy legyen. A szimuláció elindítása a korábban ismertetett módon történik. A szimuláció elindításához a Design segédablakban jelöljük be a Simulation rádiógombot, majd jelöljük ki a megjelenő "teszt_tb.vhd" fájlt. Kibontva a Isim Simulatort az alsó segédablakban, megjelenik a Simulate Behavioral Model parancs, amivel elindíthatjuk az ISE szimulátorát. A szimuláció lépéseit alul, a Console területen láthatjuk. A szimuláció során a CLK órajel, az ENABLE és a CLEAR vezérlő jelek a VHDL forrásban megadottak szerint változnak. A szimuláció eredménye egy új ablakban fog megjelenni (3.7. ábra, a képen látható eredmény a Zoom to Full View ikonra kattintás után látható). A Zoom In, Zoom Out, Zoom to Full View ikonokkal (3.7. ábra, piros téglalappal jelölt

rész) tudjuk a megjelenített időtartományt módosítani. A Restart ikon újraindítja a szimulátort, törli a megjelenített idődiagramot, Run for the time specified on toolbar ikon lenyomásakor a szimuláció a beállított időegységnyit lép előre.

3.7. ábra - A szimuláció eredménye a Xilinx ISE Simulator hullámforma ablakában.

Az egyes jelnevekre a jobb gombbal kattintva lehetőség van a kijelzés formátumát megváltoztatni. A led[7:0]

kimenet esetén ezt (jobb gomb, Radix / Hexadecimal) hexadecimálisra állítva máris könnyebben ellenőrizhető a helyes működés.

3.8. ábra - Kijelzés formátuma

Sokszor nagyon hasznos a modulok belső jeleit vizsgálni, ennek elvégzéséhez nem szükséges ezeket a jeleket kivezetni a modulból, a szimulátorban egyszerűen hozzáadhatjuk őket a Wave ablakhoz. A szimuláció a View>Panels> Instance and Process Name bal oldali ablakában megjelenik a szimulációs hierarchia, amelyben megtalálható (UUT – unit under test – néven) a tesztelés alatt álló kapcsolási rajz modul. A View>Panels>Objects ablakban látjuk a modul összes jelét, melyek közül a vizsgálni kívánt jel egyszerű drag- and-drop módszerrel adható hozzá a Wave ablakhoz (3.9. ábra). Ezután már csak a szimuláció újraindítására van szükség ahhoz, hogy a jelek értékeit figyelemmel tudjuk követni (Kék, enter-szerű gomb a felső menüben, majd

Xilinx ISE fejlesztő rendszer

a homokórás play-szerű gomb, amelyet nyomkodva, a mellette beállított értéknek megfelelő időt haladunk a szimulációban).

3.9. ábra - További jelek hozzáadása

Lehetőség van a szimulációs beállítások mentésére, ezt a File>Save paranccsal tehetjük meg. Az elmentett

„*.wcfg” fájlt a szimulátorban megnyitva, visszaállítható a korábbi konfiguráció. A szimulátor bezárásakor, ha nincs elmentve a szimulátor konfigurációja, a program megkérdezi, hogy szeretnénk e menteni a beállításokat.

3.2. Makró hozzáadása meglévő projekthez

Minden az ISE kapcsolási rajz szerkesztőjében használt makróhoz két fájl tartozik. Az egyik egy szimbólumfájl (*.sym), ami leírja a makró kapcsolási rajzon való megjelenését. A másik a működést leíró fájl, ami lehet kapcsolási rajz (*.sch), vagy HDL (*.vhd) alapú. Ha makrót akarunk a rajzból készíteni későbbi felhasználásra, akkor a portok be- és kimenetekre történő hozzáadása után, a Design ablak alsó Processes részén kibontva a Design Utilities menü-pontot rá kell kattintanunk a Create Schematic Symbol-ra. Az eddigi rajz neve alatt egy új elem jelenik meg, amit egy másik rajzra le is tehetünk. Ha rögtön makrót akarunk készíteni, akkor más az eljárás. A Project Navigator-ban, kiválasztva a Project > New Source menüpontot, megjelenik a New Source Wizard ablak. A forrás típusaként kiválasztjuk a rajzot (Schematic), megadjuk a fájl nevét és helyét majd a Next és Finish megnyomása után hozzáadódik a projekthez és megnyílik az adott nevű üres rajz. Ezután i/o portokat kell a rajzhoz hozzáadnunk a Tools > Create I/O Markers segítségével. A megjelenő dialógus dobozba be kell írni sorban, vesszővel elválasztva, az összes bemeneti, kimeneti és esetleg kétirányú port nevét. Az üres rajzon megjelennek a portok, ezután hozzárajzoljuk a makró többi részét. Ha kész, el kell mentenünk.

3.2.3.2.1. Példa kapcsolási rajz alapú makró készítésére

A következő példa során a korábbi négybites számlálót felhasználva készítjük el a makrónkat, így később lehetőség nyílik rá, hogy a számlálót önálló szimbólumként kezeljük. A 3.10. ábra szerint módosítsuk az előző feladatban szereplő számlálót. A korábbi kapcsolási rajzhoz képest csak a kimeneti busz szélessége változott, valamint a ki és bemeneti portokon csak IO markerek találhatóak. Az IO markereket a "ADD" I/O Marker" nevű gombbal lehet hozzáadni. IBUF-ra és OBUF-ra csak olyan portok esetén van szükség ami a külvilággal tart kapcsolatot. Az I/O markerekhez kapcsolódó vezeték neve lesz az IO marker neve és ez lesz a makró ki- és bemeneti portjának a nev is. A kapcsolási rajzot kijelölve, megjelenik a "Create Schematic Symbol" opció (3.10.

ábra). Ezt a processt futtatva elkészül a makró (létrejön egy sym kiterjesztésű fájl a kapcsolási rajz mellett).

3.10. ábra - Kapcsolási rajz módosítása

A fejlesztő környezet parancssorában a makró sikeres elkészítését a következő üzenet jelzi: "Process completed successfully". A szimbólumok között ezután már megtalálható a makró szimbólum (3.11. ábra).

3.11. ábra - Elkészült makró kiválasztása

A makró tartalmát a "View" menü "Push into Symbol" gombjával lehet megtekinteni. Előtte szükséges kijelölni a makrót, a kapcsolási rajzon! A korábbi teszt.sch fájl most szimbólum fájlként létezik, így szükséges egy új kapcsolási rajz fájl hozzáadása a projekthez, aminek adjuk a teszt_macro.sch nevet (3.12. ábra). Az új kapcsolási rajz file jelenleg nem "Top Modul", ezért módosítsuk a teszt_macro.sch fájl beállításait top modul szintűre (3.12. ábra).

3.12. ábra - Top modul

Xilinx ISE fejlesztő rendszer

3.2.3.2.2. Kapcsolási rajz alapú saját makró módosítása

Ha a változtatás nem érinti a makró ki- és bemeneti portjait, akkor a "Push into Symbol" paranccsal megnyitva lehetőség van a makró módosítására. A változásokat minden esetben el kell menteni.

Amennyiben a változás a makró megjelenésére is kihat, például új portot kell hozzáadni, törölni, vagy port nevet kell változtatni, akkor a következőképpen kell eljárni. Első lépésként meg kell nyitni a makrót tartalmazó sch fájlt. Ezt a "Push into Symbol" paranccsal, vagy a "Design" ablakban a kapcsolási rajzra kétszer kattintva lehet megtenni. Végezzük el a változtatásokat a makró fájlon. A példában a régi rajzot egészítsük ki egy új kimenettel, ami a számláló 15-ös értékét jelzi (3.13. ábra).

3.13. ábra - Kimenet

A módosítások mentése után a teszt.sch kapcsolási rajz fájlt kijelölve, a "Create Schemetic Symbol" parancs-ra jobb gombbal kattintva a "Process Properties..." opciót kiválasztva engedélyezni kell a létező szimbólumfájl felülírását, úgy hogy az "Owerwrite Existing Symbol" jelölő négyzetet bepipáljuk.

A "Run" parancs futtatásával módosul a makró megjelenését leíró szimbólum fájl. Ha valamelyik kapcsolási rajzban használunk egy ilyen makrót, amit módosítottunk, majd a makró megjelenésére kiható változtattatást hajtunk végre, a kapcsolási rajz szerkesztőben "Obsolate Symbols" ablak jelenik meg. Az "Update" paranccsal frissíthetjük a kijelölt objektumra vonatkozó módosításokat (3.14. ábra).

3.14. ábra - Kapcsolási rajz alapú makró módosítása

Ha a makró újrafordítása után nem kínálja fel a program a makró szimbólum frissítését, és a kapcsolási rajzon nem is változik meg a makró megjelenése, akkor újra kell indítani az ISE fejlesztőkörnyezetet (előtte mindent mentsünk el!). Az újraindulás után már a módosított szimbólumnak kell megjelennie (3.15. ábra).

3.15. ábra - Módosított szimbólumfájl

Xilinx ISE fejlesztő rendszer

A szimbólumfájl külső megjelenésén is lehetőség van módosítani. A kapcsolási rajzon elhelyezett teszt nevű makró fájlra jobb gombbal kattintva válasszuk a Symbol->Edit Symbol opciót (3.16. ábra).

3.16. ábra - Makró szerkesztés

3.2.3.2.3. Kapcsolási rajz alapú saját makró hozzáadása projekthez

Másoljuk át a makró fájlokat a projektkönyvtárba. A makró megjelenését és működését egy azonos nevű *.sym és egy *.sch kiterjesztésű fájl írja le. A *.sch fájlt az „Add Source” paranccsal a projekthez kell adni. Mivel korábban átmásoltuk a projektkönyvtárunkban kell lennie. Fontos, hogy a fájlok másolása után hajtsuk végre ezt a lépés. Végül a szimbólumok között megjelenik az új makró.

Lehetőség van a projekthez hozzáadott makró tartalmának megtekintésére. A makró szimbólum kijelölése után a

„View” menü „Push into Symbol” gombjára kattintva megjelenik a működést leíró fájl.

3.2.3.2.4. VHDL alapú saját makró hozzáadása projekthez

Másoljuk át a makró fájlokat a projektkönyvtárba. A makró megjelenését és működését egy azonos nevű *.sym és egy *.vhd kiterjesztésű fájl írja le. A *.vhd fájlt az „Add Source” paranccsal a projekthez kell adni. Mivel korábban átmásoltuk a projektkönyvtárunkban kell lennie. Fontos, hogy a fájlok másolása után hajtsuk végre ezt a lépés, mert az ISE ellenkező esetben a *.vhd fájlt felülírhatja egy template fájllal. Végül a szimbólumok között megjelenik az új makró.

Lehetőség van a projekthez hozzáadott makró tartalmának megtekintésére. A makró szimbólum kijelölése után a

„View” menü „Push into Symbol” gombjára kattintva megjelenik a működést leíró fájl.

3.3. Kapcsolási rajz elkészítése a makró használatával

Készítsünk egy új kapcsolási rajzot "teszt_macro.sch" néven. A 3.17. ábra szerint készítsük el a kapcsolási rajzot. Felhasználva a négybites számláló makrót, készíthetünk 8 bites számlálót. Figyeljünk rá, hogy a

"teszt_macro.sch" rajz legyen a topmodul (3.18. ábra).

3.17. ábra - 8 bites számláló kapcsolási rajza

Az áramkör szimulációját hasonló képen végezzük el, mint a 4 bites számláló esetében. A tesztfájl elkészítése után a következő VHDL kódot használjuk fel.

3.18. ábra - 8 bites számláló fájlok

vhd-3. ábra - ../sections/src/codeTestBrench3.vhd

Xilinx ISE fejlesztő rendszer

A szimuláció lefuttatása után a 3.19. ábra szerinti eredményt kell kapnunk.

3.19. ábra - 8 bites számláló szimulációs eredmény

3.4. A kapcsolás hardveres ellenőrzése

Jelöljük be az Implementation rádiógombot a Design panelen. A Project menü Add Source parancsával adjuk hozzá a projekthez a laborok során használt Basys2 fejlesztőpanel alapértelmezett lábkiosztását és a felhasználói megkötéseket (constraint-ek) tartalmazó „Basys2_100_250General.ucf” fájlt. A Megnyitás és OK gombok megnyomása után a projektben megjelenik a kiválasztott fájl, amit kettős kattintással szerkesztésre meg is nyithatunk (3.20. ábra). A fájl egyéb – itt nem részletezett – felhasználói megkötések mellett a kapcsolási rajzban használt vezetékek neveit (NET) és a hozzájuk tartozó FPGA IC kivezetések (lábak) összerendeléseit definiálja.

3.20. ábra - A „Basys2_100_250General.ucf” fájl

A "Basys2_100_250General.ucf" fájl az FPGA összes panelen bekötött kivezetéséhez alapértelmezett belső vezetékneveket rendel. Az alapértelmezett elnevezések segítenek a panelen való tájékozódásnál, azonban nincsenek összhangban a kapcsolási rajzban általunk használt I/O Marker nevekkel, emellett legtöbbjüket nem is használjuk (3.21. ábra).

vhd-4. ábra - ../sections/src/codeUcfClk4bit.vhd

Xilinx ISE fejlesztő rendszer

A helyes működéshez, módosítsuk az alapértelmezett ucf fájlt az alábbiak szerint.

3.21. ábra - UCF

Ezzel a kapcsolási rajzunk Led(7:0) kimeneteit a panelen található LED-ekhez, az ENABLE bemenetet az SW0 kapcsolóhoz a CLK és CLEAR bemeneteket pedig a BTN1 és BTN0 nyomógombokhoz rendeltük (a buszvezetékek elnevezésében szereplő zárójelek az .ucf-fájlban <> karakterekkel helyettesítendők). Az összes többi nem használt vezetékek definíciót tartalmazó sorokat a # karakterrel alakítsuk megjegyzéssé (comment), vagy töröljük. Mentsük el a változtatásokat. A kapcsolás implementálásához és az FPGA konfigurációs állományának előállításához a Design segédablakban jelöljük ki a „teszt.sch” kapcsolási rajzot. Ennek hatására a Processes ablakban az Implement Design kibontásakor megjelenik a Generate Programming File parancs, amelynek feladata, hogy létrehozza az FPGA-ba letölthető „teszt.bit” állományt. Ez általában elég sokáig tart, a művelet lépéseit a Console területen követhetjük. Először a parancs futtatásának eredménye hibaüzenet, amit az Errors ablakban tekinthetünk meg. Mivel a kapcsolásban a tárolók órajele nem dedikált órajel vezetéken keresztül kerül az FPGA-ba, a program figyelmeztet. Mivel esetünkben ez a nem optimális vezetékezés elfogadható, az ucf-fájlban el kell helyeznünk a

NET "CLK" CLOCK_DEDICATED_ROUTE = FALSE;

kiegészítést. Az újabb Generate Programming File parancs futtatásakor a fenti hibajelzés már csak a Warnings ablakban jelenik meg. Az elkészült konfigurációs állományt („teszt.bit”) a korábban ismertetett Adept program segítségével letölthetjük az FPGA-ba.

3.4.3.4.1. A konfigurációs fájl letöltése az FPGA-ba

Először telepíteni kell az Adept kezelő programot (jelenleg digilent.adept.system_v2.8.1.exe), ezt még azelőtt kell megtenni, mielőtt a tesztkártyát az PC-hez csatlakoztatnánk. Csatlakoztatáskor a Windows észreveszi az új hardvert, engedélyezni kell a driver telepítését. Az Adept indulásakor észreveszi, hogy melyik eszköz van csatlakoztatva. A Config fül kiválasztásával Browse-ra kattintva kikeressük az adott bit kiterjesztésű fájlunkat és bevisszük az FPGA melletti edit box-ba. A Program gombra kattintva megtörténik a letöltés, és a kártyán azt látjuk, ami sikerült.

3.5. Az órajel bemenet prellmentesítése

A prellezés (a mechanikusan működő villamos érintkezők egymáson való pattogása) miatt az órajelet szolgáltató BTN1 nyomógomb nem mindig ad rögtön stabil jelet. Rövid ideig egyszeri lenyomás hatására is két állapot között „pereg”, ezzel többszöri 0 -> 1 átmenetet adhat a tárolók órajel bemenetére. Ennek a jelenségnek a kiküszöbölésére módosítsuk a kapcsolást a 3.22. ábra szerint, az ucf-fájlt pedig az alábbiak szerint.

vhd-5. ábra - ../sections/src/codeUcfClkPrell.vhd

Az aszinkron törlés és beállítás (CLR, PRE) bemenetekkel rendelkező FDCP flip-flop az UP bemenetre csatlakozó BTN3 nyomógomb megnyomásával (preset) logikai 1 szintre vált, a DOWN bemenetre csatlakozó BTN2 nyomógomb megnyomásával (clear) pedig logikai 0 szintre vált. Egy teljes órajel periódust (felfutó él - lefutó él) a BTN3 és BTN2 nyomógombok egymás utáni lenyomásával hozhatunk létre.

3.22. ábra - A „teszt.sch” kapcsolási rajz módosítása

4. fejezet - Egyszerű kombinációs hálózatok

4.1. Multiplexer, demultiplexer

4.1.4.1.1. Multiplexer

A multiplexer egy olyan áramkör, amely több bemenet közül egyet enged tovább a kimenetén, méghozzá azt a bemenetet, amelynek a címe rákerül a címző bemenetre. Ez a leggyakrabban használt kombinációs hálózat.

4.1.4.1.1.4.1.1.1. 2 bemenetű multiplexer

Legegyszerűbb esetben a cím egybites „select” jel (S), ami két bemenet közül (I0, I1) választ ki egyet (4.1. ábra, 4.2. ábra). A két bemenetű multiplexer igazságtáblája a következő:

4.1. táblázat - Egybemenetű multiplexer igazságtáblázata

SY 0I

0 1I 1

4.1. ábra - Két bemenetű multiplexer kapcsolási rajza

4.2. ábra - Két bemenetű multiplexer logikai rajza

A multiplexert legtöbbször bonyolult adatutak kialakítására használják pl. a processzorok ALU-jában. Vannak egyéb alkalmazási, ezek közül először kettőt mutatunk meg.

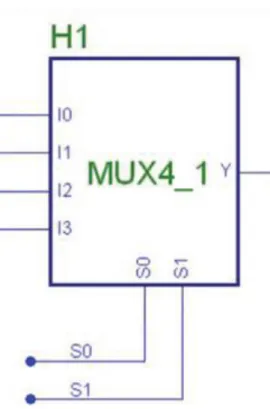

4.1.4.1.1.4.1.1.2. 4 bemenetű multiplexer

A multiplexer címbitjeinek eggyel való megnövelése a bemenetek számának a kétszeresét teszi lehetővé. Így két címbit esetén kapjuk a 4-bemenetű multiplexert (4.3. ábra, 4.4. ábra). A négy bemenetű multiplexer igazságtáblája a következő:

4.2. táblázat - Kétbemenetű multiplexer igazságtáblázata

S 1 S 0 Y

00I 0 01I 1 10I 2 11I 3

4.3. ábra - Négy bemenetű multiplexer logikai rajza

Egyszerű kombinációs hálózatok

4.4. ábra - Négy bemenetű multiplexer kapcsolási rajza

A nagyobb számú bemenetekkel rendelkező multiplexer tervezése kétféleképpen lehetséges: a megfelelő számú kapuból megtervezve, vagy kisebb multiplexerek felhasználásával. Például egy 16 bemenetű multiplexert így is megtervezhetünk. Ez ugyan redundáns a felhasznált kapuk számát illetően, de lehet, hogy az alkatrészkészlet ezt a megoldást teszi alkalmasabbá (4.5. ábra).

4.5. ábra - 16 bemenetű multiplexer tervezése kisebb multiplexerek felhasználásával

Egyszerű kombinációs hálózatok

A multiplexer lehetőséget nyújt look-up table megvalósítására (4.6. ábra). Az általunk használt FPGA CLB- jében 4-bemenetű LUT található tetszőleges 4-változós logikai függvény előállítására. Ha ezt egy tárolóval oldanák meg, minden egyesCLB-ben egy 64K bites tárolóra lenne szükség az összes logikai függvény előállítására. Ehelyett pl. egy 16 bites regiszter és egy 16 bemenetű multiplexer elegendő. A multiplexer címbitjeire csatlakozik az adott logikai függvény 4 változója. A rajz alapján a szoftver kiszámolja, hogy melyik logikai függvény kell a megvalósításhoz, és a 4 bemenet összes kombinációjának megfelelő 16 kimeneti bitet betölti egy 16 bites regiszterbe, amelynek kimenetei csatlakoznak a multiplexer megfelelő címzésű bemenetéhez. Látható, hogy egy ilyen megoldás erőforrás igénye lényegesen kisebb.

4.6. ábra - Look-up table megvalósítása multiplexer segítségével

4.1.4.1.2. Latch

A latch egy olyan tároló elem, amely nem órajelre (élre) működik, hanem egy engedélyező jel megléte esetén az áramkör transzparens, azaz átengedi a bemenetén lévő jelet, az engedélyező jel megszűnésére az utolsó értéket tárolja. Az alábbi rajzon az engedélyező jel aktív értéke az első esetben magas, a másik esetben alacsony (4.7.

ábra).

4.7. ábra - Latch

4.1.4.1.3. Korrekt flip-flop órajel engedélyezés

Egyszerű kombinációs hálózatok

Az órajelre működő szinkron hálózatok esetén fontos, hogy az összes tároló egyszerre billenjen, ellenkező esetben rövid időre hazárd állapotok léphetnek fel. Ezenkívül a dinamikus bemeneten a jelnek stabilnak kell lennie bizonyos idővel az órajel felfutása előtt és után. Ez az áramkörre jellemző katalógus érték (setup time, hold time). Ha ezek a feltételek nem teljesülnek a flip-flop működése bizonytalanná válik, ha például az órajelet kapuzzuk, így plusz késleltetést viszünk bele. Ezért a korrekt megoldást egy multiplexeren áthaladó enable jel biztosítja (4.8. ábra). az első esetben egy D flip-flop, a másodikban egy T flip-flop esetében. Az első esetben, ha az órajel nincs engedélyezve, az órajelre saját magát írja be újra meg újra, ugyanaz a hatás, mintha nem lenne órajel. A második esetben a bemenetre 0 kerül, így a T flip-flop nem billen.

4.8. ábra - Korrekt flip-flop órajel engedélyezés

4.1.4.1.4. Demultiplexer

A demultiplexer működése a multiplexerének a fordítottja. Egy bemenete van, és a címző bemenetek határozzák meg, hogy melyik kimeneten megy ki a jel (4.9. ábra, 4.10. ábra). A többi kimenet állapota inaktív. A felhasználási területe főként a számítástechnika.

4.9. ábra - Négy kimenetű demultiplexer

4.10. ábra - Négy kimenetű demultiplexer kapcsolási rajza

4.1.4.1.5. Laborfeladat

Tervezzen meg egy 8-bemenetű multiplexert. Az adatbemeneteket a Digilent Basys2 kártyán lévő SW0-SW7 kapcsolókon lehessen beállítani, a címző bemeneteket a multiplexer bemenetére csatlakozó 3-bites számláló

Egyszerű kombinációs hálózatok

számláló kimeneteinek indexének. Végezze el az áramkör szimulációját, és ha jó, fordítsa le, a kapott bit kiterjesztésű fájlt töltse le a Basys2 kártyába, és a kapcsolók és az órajel nyomógomb segítségével próbálja ki az áramkör működését.

4.1.4.1.5.4.1.5.1. Alkalmazandó műszerek és eszközök

• PC számítógép

• Digilent Basys2 Spartan-3E FPGA mérőpanel

• Digilent Adept konfiguráló szoftver

4.2. Kódolók

4.2.4.2.1. Komparátorok (Magnitude Comparators)

A digitális komparátorok 2 azonos bitszélességű bináris értéket hasonlítanak össze, egyszerűbb esetben csak az egyenlőséget jelezve, de az un. magnitude komparátorok ezen kívül a kisebb-nagyobb relációt is jelzik (4.11.

ábra).

4.11. ábra - 2-szer 4-bites komparátor blokkrajza

A két bemenet A(3:0) és B(3:0), az EQ kimenet igaz volta az egyenlőséget (equal), a BGA a B(3:0) a nagyobb voltát, (B greater), az AGB az A(3:0) nagyobb relációt jelenti. A relációt a legnagyobb helyi érték dönti el, ha egyenlők, akkor a következő helyi érték, stb. (4.3. táblázat)

4.3. táblázat - Magnitude Comparator igazságtáblázata

A 3

B 3

A 2

B 2

A 1

B 1

A 0

B 0

A G B B G A E Q

10xxxxxx100 01xxxxxx010

==10xxxx100

==01xxxx010

====10xx100

====01xx010

======10100

======01010

========001

Miután az A nagyobb, a B nagyobb és A=B relációk egymást kizárják, ezért az előző igazságtábla redundáns, egyszerűsíthető (4.4. táblázat). Így, ha AGB=0 és EQ=0, akkor BGA=1 (4.12. ábra).

4.4. táblázat - Magnitude Comparator egyszerűsített igazságtáblázata

A 3

B 3

A 2

B 2

A 1

B 1

A 0

B 0

A G B E Q

10xxxxxx10

==10xxxx10

====10xx10

======1010

========01

4.12. ábra - Magnitude Comparator egy áramköri megvalósítása

Egyszerű kombinációs hálózatok

4.2.4.2.2. Enkóderek

Az encoder (átkódoló, kódoló stb.) egy olyan áramkör, amely az információt valamely formából valamilyen másikba alakítja át. (Természetesen, van sokkal precízebb definíció is). Mi két átkódolóval foglalkozunk, az egyszerű átkódolóval és a priority átkódolóval.

Az egyszerű átkódoló a sorszámozott egyedi bemeneteket (one hot) átkódolja a sorszám (v. index) bináris kódjává (4.5. táblázat, 4.13. ábra). A bemenetek közül egy és csakis egy lehet aktív. Az áramkör nem tudja megkülönböztetni azt, hogy az I0 bemenet van, vagy egy bemenet sincs.

4.5. táblázat - 8-ról 3-ra enkóder igazságtáblázata

Y 2

Y 1

Y 0 I n 0

000

I n 1

001

I n 2

010

I n 3

011

I n

100

![2.4. ábra - A szeletek összetevői [2]](https://thumb-eu.123doks.com/thumbv2/9dokorg/1105355.76828/17.892.310.583.110.581/ábra-a-szeletek-összetevői.webp)